Coreinfo を使うと仮想化に対応しているかなどCPU が対応している命令などを調べることができる。

Coreinfo は、論理プロセッサと物理プロセッサの間のマッピング、NUMA ノードと NUMA ノードが存在するソケット間のマッピング、および各論理プロセッサに割り当てられたキャッシュを確認できるコマンド ライン ユーティリティです。Windows の GetLogicalProcessorInformation 関数を使用してこの情報を取得し、論理プロセッサに対するマッピングをアスタリスク (*) で表して画面に出力します。Coreinfo は、システムのプロセッサとキャッシュ トポロジを把握するのに役立ちます。(「Coreinfo」より引用)

ダウンロード

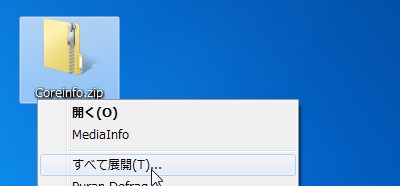

「Coreinfo」から「Coreinfo.zip」をダウンロードする。

スポンサードリンク

ダウンロードした「Coreinfo.zip」を解凍する。

使い方

コマンドプロンプトから「Coreinfo.exe」を実行する。

実行例

Coreinfo v3.04 - Dump information on system CPU and memory topology Copyright (C) 2008-2012 Mark Russinovich Sysinternals - www.sysinternals.com Intel(R) Pentium(R) CPU G6950 @ 2.80GHz Intel64 Family 6 Model 37 Stepping 5, GenuineIntel HTT * Hyperthreading enabled HYPERVISOR - Hypervisor is present VMX * Supports Intel hardware-assisted virtualization SVM - Supports AMD hardware-assisted virtualization EM64T * Supports 64-bit mode SMX - Supports Intel trusted execution SKINIT - Supports AMD SKINIT EIST * Supports Enhanced Intel Speedstep NX * Supports no-execute page protection PAGE1GB - Supports 1 GB large pages PAE * Supports > 32-bit physical addresses PAT * Supports Page Attribute Table PSE * Supports 4 MB pages PSE36 * Supports > 32-bit address 4 MB pages PGE * Supports global bit in page tables SS * Supports bus snooping for cache operations VME * Supports Virtual-8086 mode FPU * Implements i387 floating point instructions MMX * Supports MMX instruction set MMXEXT - Implements AMD MMX extensions 3DNOW - Supports 3DNow! instructions 3DNOWEXT - Supports 3DNow! extension instructions SSE * Supports Streaming SIMD Extensions SSE2 * Supports Streaming SIMD Extensions 2 SSE3 * Supports Streaming SIMD Extensions 3 SSSE3 * Supports Supplemental SIMD Extensions 3 SSE4.1 - Supports Streaming SIMD Extensions 4.1 SSE4.2 - Supports Streaming SIMD Extensions 4.2 AES - Supports AES extensions AVX - Supports AVX intruction extensions FMA - Supports FMA extensions using YMM state MSR * Implements RDMSR/WRMSR instructions MTTR * Supports Memory Type Range Registers XSAVE - Supports XSAVE/XRSTOR instructions OSXSAVE - Supports XSETBV/XGETBV instructions CMOV * Supports CMOVcc instruction CLFSH * Supports CLFLUSH instruction CX8 * Supports compare and exchange 8-byte instructions CX16 * Supprots CMPXCHG16B instruction DCA - Supports prefetch from memory-mapped device F16C - Supports half-precision instruction FXSR * Supports FXSAVE/FXSTOR instructions FFXSR - Supports optimized FXSAVE/FSRSTOR instruction MONITOR * Supports MONITOR and MWAIT instructions MOVBE - Supports MOVBE instruction PCLULDQ - Supports PCLMULDQ instruction POPCNT * Supports POPCNT instruction SEP * Supports fast system call instructions DE * Supports I/O breakpoints including CR4.DE DTES64 * Can write history of 64-bit branch addresses DS * Implements memory-resident debug buffer DS-CPL * Supports Debug Store feature with CPL PCID * Supports PCIDs and settable CR4.PCIDE PDCM * Supports Performance Capabilities MSR RDTSCP * Supports RDTSCP instruction TSC * Supports RDTSC instruction TSC-DEADLINE - Local APIC supports one-shot deadline timer TSC-INVARIANT * TSC runs at constant rate xTPR * Supports disabling task priority messages ACPI * Implements MSR for power management TM * Implements thermal monitor circuitry TM2 * Implements Thermal Monitor 2 control APIC * Implements software-accessible local APIC x2APIC - Supports x2APIC CNXT-ID - L1 data cache mode adaptive or BIOS MCE * Supports Machine Check, INT18 and CR4.MCE MCA * Implements Machine Check Architecture PBE * Supports use of FERR#/PBE# pin PSN - Implements 96-bit processor serial number Logical to Physical Processor Map: *- Physical Processor 0 -* Physical Processor 1 Logical Processor to Socket Map: ** Socket 0 Logical Processor to NUMA Node Map: ** NUMA Node 0 Logical Processor to Cache Map: *- Data Cache 0, Level 1, 32 KB, Assoc 8, LineSize 64 *- Instruction Cache 0, Level 1, 32 KB, Assoc 4, LineSize 64 *- Unified Cache 0, Level 2, 256 KB, Assoc 8, LineSize 64 -* Data Cache 1, Level 1, 32 KB, Assoc 8, LineSize 64 -* Instruction Cache 1, Level 1, 32 KB, Assoc 4, LineSize 64 -* Unified Cache 1, Level 2, 256 KB, Assoc 8, LineSize 64 ** Unified Cache 2, Level 3, 3 MB, Assoc 12, LineSize 64 Logical Processor to Group Map: ** Group 0

参考文献

スポンサードリンク

コメント